Currently, with the gradual approach of the limits of Moore's Law, the chip manufacturing industry has crossed the 3-nanometer node and is moving towards the 2-nanometer direction. This technological evolution brings not only the reduction of node size but also the ultimate pursuit of integration, power consumption, and performance. Against this increasingly challenging backdrop, chip designers are facing unprecedented pressures and opportunities.

At the same time, memory technology, as an important part of chip design, has also received great attention and challenges. The emergence of NVM IP technology has provided a powerful way to solve these challenges. Compared with the eFuse provided by traditional wafer processes, NVM IP has become an indispensable part of advanced node design with its advantages such as higher density, lower power consumption, and faster speed.

However, integrating NVM IP technology effectively into the design of advanced nodes is not an easy task.

The Development and Role of NVM

NVM refers to Non-Volatile Memory, a storage technology that can save data for a long time without continuous power supply. Unlike volatile memory (such as RAM), NVM can keep data intact even when the power is off. This makes it very useful in many applications, such as computer boot programs, firmware, embedded systems, and storage in mobile devices.

In the early days, the main NVM used in chip design was E-square (EEPROM) and Flash memory, which increased the process complexity. Later, new non-volatile memory technologies continued to emerge to meet the growing market demand and technical challenges. NVM technologies include AntiFuse OTP and EEPROM that do not increase process, which have improved in terms of power consumption, speed, density, and durability.

Advertisement

With the emergence of new NVM technologies, the corresponding NVM IP has been generated. Embedded NVM IP refers to the non-volatile memory integrated in the chip, which can be configured according to the application requirements. The NVM IP core can be used for product ID recognition, defect repair, storage configuration data, program code, keys, calibration parameters, etc., without the need for external components.

At present, NVM IP can be roughly classified into OTP (One-Time Programming), MTP (Multiple-Time Programming), and FTP (Few-Time Programming). The reasons behind the development are as follows:

With the increase of chip functions, in the era of the network, security is becoming more and more important, and the changes and development of chip storage solutions are needed. The eFuse storage solution provided by the wafer factory, which originally relied on, gradually cannot meet the application needs due to high cost, slow read and write speed, low security, lack of flexibility, and potential reliability issues. Therefore, OTP IP (One-Time Programmable Intellectual Property) was first developed to replace eFuse/mask ROM.

Compared with eFuse and mask ROM, OTP IP has better power consumption, performance, and area (PPA), and can achieve higher capacity, ranging from 256Kb to 1Mb. Unlike eFuse, OTP IP allows programming during the production process, making it more flexible and able to meet the data storage needs of applications such as microcontrollers (MCU). At the same time, OTP IP is also more suitable for security applications and key storage, which is more reliable than eFuse.Subsequently, MTP (Multiple Times Programmable) and eFlash, which can meet the requirements for multiple updates, have gradually matured and expanded to various wafer process nodes. This has enabled the realization of many diverse functions and allowed the original external ROM/EEPROM to be miniaturized into the chip, reducing costs and improving the integration and performance of the chip.

Today, NVM IP has become indispensable in many applications, such as panel driver ICs (DDIC/TDDI), power management ICs (PMIC), and image display chips (CIS), all of which require the use of OTP/MTP. Specifically, OTP is mainly used for one-time programming scenarios, suitable for one-time correction, ID recording, and security keys; MTP can be used for data programming scenarios that require frequent updates, such as Bluetooth chips, DDR5 SPD, etc., which require 10K to 100K data updates; FTP can be used for scenarios that require multiple calibration parameters, such as power management ICs and other applications dominated by analog circuits.

At present, Synopsys is one of the few companies in the industry that has launched a mature and comprehensive NVM IP solution. Since NVM does not allow any data errors or loss, rigorous functional verification must be completed during the development process. It takes one to two years from development to design verification, and after the process is verified in the wafer factory, it can be provided for customer use. In addition to many advantages, the cost of NVM IP is relatively high. The advantage of Synopsys' NVM solution is that it can provide NVM built on the wafer factory's standard process without increasing the photomask, effectively balancing cost and performance.

In the OTP part, Synopsys provides antifuse OTP solutions from 0.18um to the most advanced process N4P (N3P under development), supporting large capacity while also built-in Charge Pump, which can meet the programming needs from production testing to customer application ends, and also has the best reliability and security.

In terms of MTP, Synopsys provides solutions from 0.18um to 40nm, which can meet the application requirements of a few to 400K updates, support a maximum capacity of 8Kb, and can operate at 5V, 3.3V, and even the industry's only 2.5V MTP solution. It also supports RFID applications, achieving ultra-low power consumption with all operations below 10uA. There is no MTP solution below 40nm.

The development of NVM IP has brought new opportunities to the field of embedded storage and provided developers with more choices to meet their application needs. However, there are also challenges on the road ahead for NVM IP.

Emerging markets and advanced processes put forward higher requirements for NVM IP

With the growing demand for secure storage of sensitive data in high-performance computing (HPC), the Internet of Things, and artificial intelligence chips, embedded non-volatile memory (eNVM) has been increasingly widely used in advanced node chips in these emerging markets. However, advanced processes also bring new challenges, such as the rise in mask composition costs and wafer average selling price (WASP), making the reliability and high yield of embedded NVM IP more important.

Starting from the FinFET process node, the development of OTP also faces more challenges and extends the development and verification cycle. To avoid the situation where process fine-tuning causes NVM to be redesigned, wafer factories require OTP development to be allowed only after the process is stable, which extends the timeline for the launch of OTP.In addition, with the continuous miniaturization of process technology, the area of OTP has been significantly reduced accordingly. However, the programming process of anti-fuses requires the use of a charge pump to generate high voltage. In advanced processes, the I/O voltage has been reduced to 1.8V or 1.2V, and with the development of FinFET technology, it has further decreased to the GAA (Gate-All-Around) process node, where there are no available I/O components. Therefore, it is necessary to rely on core devices to develop charge pumps and their peripheral circuits to ensure that reliable OTP is still available on these advanced processes. This design method that relies on core devices makes OTP a nearly boutique process unique to itself.

Synopsys' OTP solution has three layers of insurance to ensure the best yield and reliability: it includes the use of double physical cells to provide double protection for each bit; it also allows for error correction within the same I/O unit for one bit; and there are reserved repair blocks that can replace more than one bit of defects.

Furthermore, the solution includes ECC (Error-Correcting Code) as a standard preset, allowing users to choose to enable or disable it according to their needs. This makes the solution not only suitable for general consumer applications but also meets the needs of high-reliability fields such as industrial control, automotive electronics, and data centers.

It is worth mentioning that Synopsys' OTP solution can not only ensure high yield during programming in the factory but also achieve the best yield during application-side programming. This design avoids the risk of chip scrapping due to OTP programming failure, greatly improving the overall reliability and service life of the chip.

Synopsys' OTP Solution on TSMC 5nm

Synopsys' OTP solution has been verified on TSMC N5 process and has obtained TSMC IP9000 certification. This OTP IP provides a stable and efficient storage solution in various applications through multi-layer metal processes, extended voltage support, and various programming options.

The following figure shows the implementation of Synopsys OTP IP on TSMC N5 process (IP9000) and describes its features and functions in detail. The logic bit/data width range of Synopsys' OTP solution is from 16Kb to 128Kb, using an 8-layer metal process, and an RTL controller with an internal APB bus interface, which is convenient for customers to integrate without the need to develop their own control modules.

Features and Functions of Synopsys OTP IP

In addition, OTP has multiple security features, including an independent read interface, word-level and macro-level programming and read locking, ensuring that data will not be misoperated during power-on, and each I/O address supports read or write locking functions. At the same time, it can detect abnormal voltages to prevent hackers from bypassing or stealing OTP data or security keys.

During TSMC's characteristic testing process, Synopsys' OTP IP demonstrated excellent yield and reliability and can operate stably under process, voltage, and temperature (PVT) conditions.The silicon wafer characteristic test results under the TT, FF, SS, FS, and SF process branches show that the OTP IP can almost achieve 100% input and programming yield. Among the approximately 1200Mb tested, only one bit failed, but it has been successfully repaired. Compared with the previous OTP technology, the new OTP technology has significantly improved efficiency in single-pulse programming (only 17 bits failed in 360Mb). It can read from the core voltage (VDD) without the need for a read regulator. The characteristics have been characterized over a wide range of VDDIO voltages to ensure voltage adaptability.

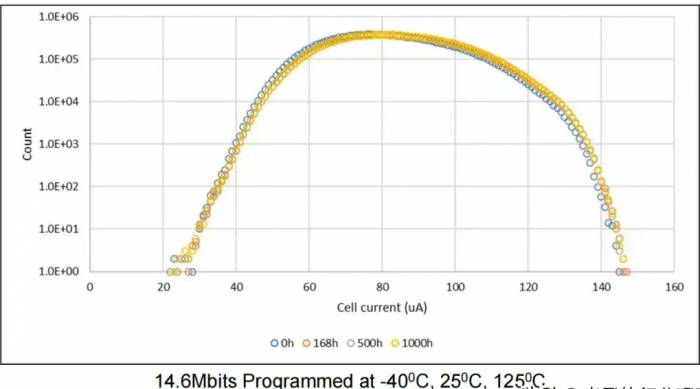

In addition, the OTP solution has undergone silicon wafer qualification from three non-consecutive batches, and the results show: the performance of the OTP IP under high-temperature storage life (HTSL) and high-temperature operation life (HTOL) conditions is quite excellent. The HTSL test temperature is 150°C (Figure a), and the HTOL test temperature is 125°C (Figure b); all read points did not show bit cell degradation (Figure c), ensuring the long-term reliability of the data; qualification has been completed without the need for ECC (error correction code), further simplifying the design and use.

Conclusion

In the evolution process of the semiconductor industry, the application of NVM IP technology has brought unprecedented opportunities and challenges to chip designers. By breaking through the limitations of traditional memory technology, NVM IP technology makes it possible to achieve higher performance and functions on a smaller scale, promoting chip design into a new era.

In the wave of this transformation, Synopsys' NVM IP, with its secure, reliable, and high-yield characteristics, provides a comprehensive NVM solution for emerging markets and advanced processes. Looking forward, NVM IP technology will continue to play an important role, leading chip design to continuously innovate and promote the development of the semiconductor industry.

On June 21, Synopsys will bring a dry goods sharing on how to use NVM in SoC design. Welcome to register and sign up to explore with us!

Comments